# TH6503

## **USB Low-Speed Interface**

Description

The TH6503 is an integrated circuit which enables the Universal Serial Bus (USB) to be connected to a microcontroller. The interface module contains all the components required to transmit data via the USB.

The TH6503 has been developed for applications requiring a low speed interface to the USB. Any microcontroller can be used for control purposes. In addition to the default endpoint 0 for control transfer up to two endpoints can be supported by TH6503. The TH6503 has been developed in conformity with USB Specifications 1.1.

#### Features

- S Complient with USB Specification 1.1

- Supports up to three programmable endpoints (3.3 volts or 5 volts)

for interrupt and control transfer in each direction

Integrated oscillator for clock generation,

- S Data transfer at USB low speed

- Supports suspend mode

- S Universal serial microcontroller interface

- z Register programmable

- Programmable 1.5 MHz to 6 MHz out clock for microcontroller

#### Provides power supply for the microcontroller (3.3 volts or 5 volts)

- Integrated oscillator for clock generation, supports 6 MHz quartz, ceramic resonator or external clock input

- Simple external circuitry

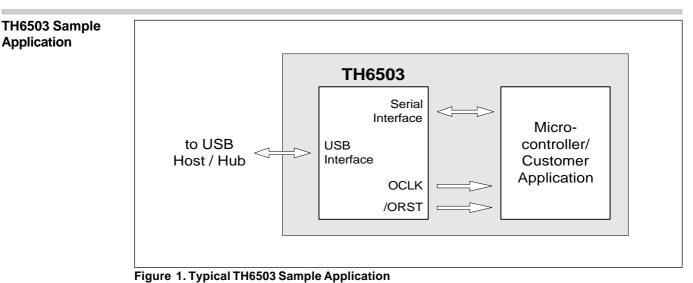

Figure 1 demonstrates a typical TH6503 application. The TH6503 translates the data and control signals received from the USB in a serial format which can be read by the microcontroller. The data is stored in a FIFO buffer and can be called up from a standard microcontroller via a register programmable serial interface at any time and processed further. Data generated by peripheries is passed to the TH6503 with the same protocol and stored in a FIFO buffer until it is collected by the USB. The TH6503 translates all the data in the USB-specific format and generates the necessary control signals. The TH6503 requires a minimum number of external elements and can easily be implemented in a circuitry. It provides an external clock which can be used to activate a microcontroller.

#### Function USB Data Transmission

TH6503/

The TH6503 supports the USB Specification 1.1 data model.

Data from the USB host to the device and vice versa is transmitted serially. The data are NRZI coded to increase transmission reliability; bit stuffing (inserting an extra 0 bit after any 6 consecutive 1 bits) is performed and a CRC check carried out. Bit stuffing, NRZI coding/decoding and CRC checks or generation are performed within the TH6503.

The data is transmitted in packets. Three types of packets are defined for the USB: token, data and handshake.

The token is always passed on by the host. It contains a PID (packet identifier) which defines the direction of the following data transmission and the address of the device and endpoints to be addressed.

Depending on the previous token command, data is transferred from the USB host to the TH6503 (OUT transfer) or transferred from the TH6503 to the USB host (IN transfer). In the process the respective FIFOs are written (OUT) or read (IN).

The data transfer is concluded with a handshake. If the data has been received successfully, an ACK is sent to the data source. If no data is ready for an IN transfer out of the TH6503, it sends an NAK handshake instead of the data (if endpoint is enabled).

#### Figure 2. Data Flow

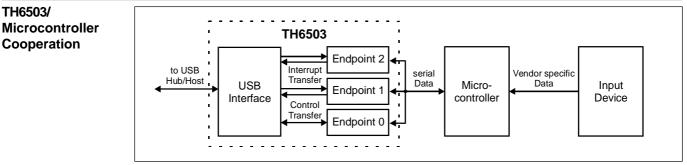

The TH6503 is responsible for the data flow between the USB and the microcontroller. It ensures that the USB transfers the data in line with the protocol. All information in the protocol layer is decoded by the TH6503 and carried out accordinaly.

The data arriving from the USB host is stored in a FIFO buffer until it is collected by the microcontroller. Data transmitted to the USB host are imported from a FIFO buffer which has previously been filled by the microcontroller. A /INT signal signals to the microcontroller that the FIFO status has been changed by USB.

Data is transferred between the microcontroller and the TH6503 via a software-emulating serial interface controlled by the microcontroller.

As the TH6503 cannot interpret the content of the data, it must be evaluated within the microcontroller. This also applies to USB-specific control information. All USB-typical descriptors and the associated requests must be created and managed by the microcontroller.

The setting of the USB address serves here as an example. After resetting the USB, the address is set to the default value 0 (USBAddressRegister). A specific address is transferred from the USB host software to the device with the SET\_ADDRESS

command. This command. like all SET and GET commands, can only be decoded by the microcontroller. The USB address is decoded in the TH6503 with the aid of the USB AddressRegister. For this reason the microcontroller must write the USB address determined in this register.

The TH6503 supports the USB suspend mode. Control takes place via the microcontroller. The ACT bit can be used in the StatusRegister <5> which is set on the USB for each activity. If this bit has been inactive for a longer period of time (3 ms), the microcontroller can set the TH6503 and itself in the suspend mode using the SUS bit in the BridgeConfigRegister <4>. The suspend mode can be ended using the software or an external signal. Apart from the suspend mode, the TH6503 also supports a number of other power saving modes which either stop the microcontroller by switching off the clock or set the whole USB bridge in a power saving mode.

The TH6503 provides the clock pulse for the microcontroller. It can be programmed with the OCR 1 - OCR 0 bits in the BridgeConfigRegister <1-0>.

The TH6503 supplies 3.3V voltage to power the microcontroller; this is produced by the adjacent 5V bus power supply connection.

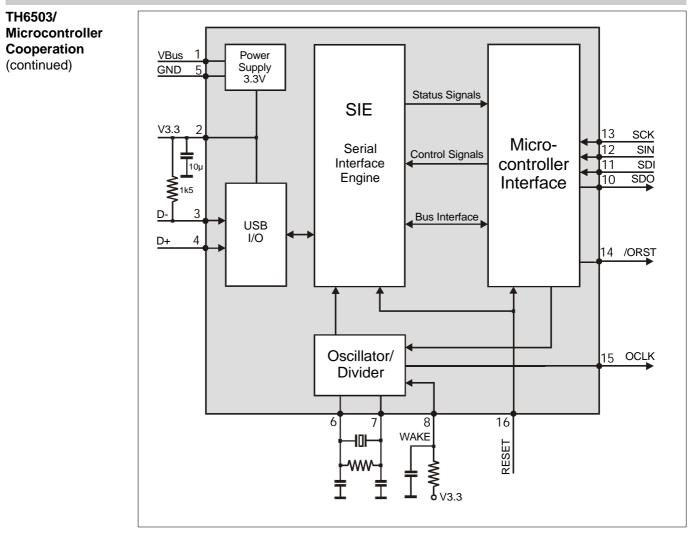

Figure 3. TH6503 Block Diagram

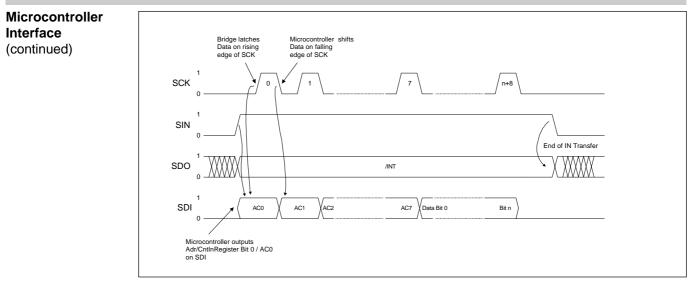

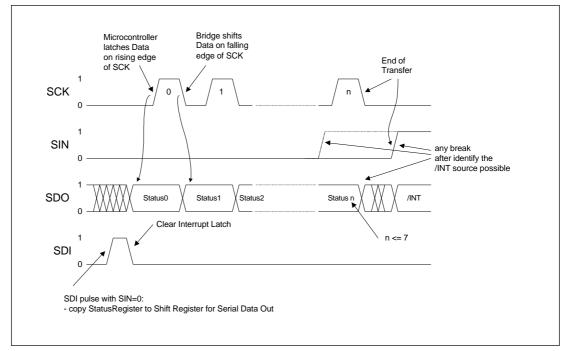

| Microcontroller<br>Interface | The data is transferred between the microcontroller and the USB bridge using the clock (SCK) generated by the microcontroller asynchronous to the USB clock.                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|                              | Data IN Transfer<br>(from the microcontroller to the TH6503)                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

|                              | Data IN transfer is initiated with rising SIN edge (IN packet sync). Data is transferred via the SDI pin.                                                                                                                                                                                                                                                 | If a register is the target of the data IN transfer the bits IC3-IC0 and TI have no meaning.                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

|                              | Initially the Adr/CntInRegister which indicates the internal address in the TH6503 is written. Data is subsequently transferred beginning with byte 0 to Byten LSB first. Bits IC3-IC0 in the Adr/CntInRegister <3-0> contain the information on the number of bytes to be transferred to the USB host if the target of the data transfer was an IN FIFO. | With falling SCK edge the microcontroller trans-<br>mit the bits to SDI and the bits are imported from<br>the bridge with increasing SCK edge. After each<br>transmission of 8 bits the respective IN FIFO value<br>is increased by 1. If the microcontroller writes<br>more data than indicated in the Adr/CntInRegister,<br>the oldest data are overwritten. After the final |  |  |  |  |  |  |

|                              | A zero data transfer is identified with reset of IC3-<br>IC0 bits after writing the Adr/CntInRegister one<br>additional clock on SCK must be generated.                                                                                                                                                                                                   | falling edge of SCK first SDI and then SIN must be<br>reset to 0 to terminate the transfer. The associated<br>IN Done bit in the StatusRegister is reset automati-<br>cally to enable USB IN transfer.                                                                                                                                                                         |  |  |  |  |  |  |

3

Figure 4. Serial Data IN

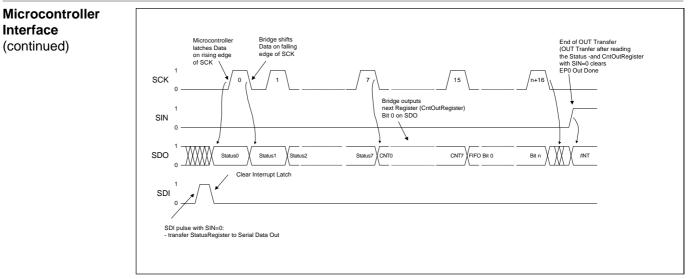

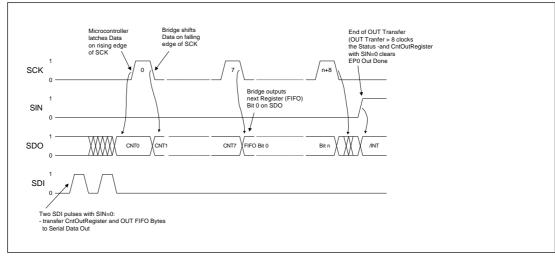

#### **Data OUT Transfer**

(from the TH6503 to the microcontroller)

An impulse on the SDI link at SIN = 0 represents the OUT packet sync for an OUT transfer. With the falling SCK edge the data (LSB first) is shifted to SDO and with rising SCK edge accepted by the microcontroller. The StatusRegister is transferred initially followed by the CntOutRegister and finally the OUT FIFO data. If the transfer is terminated after less than 8 clock pulses, only single StatusRegister bits are read. Linear transfer is interrupted by SIN = 1 and must be initiated with a new OUT packet sync at SIN = 0. Two impulses on the SDI link initiate a transfer of the CntOutRegisters and of the following OUT FIFO bytes without the StatusRegister. A zero data transfer is identified by an OUT Count Byte value of 0. The end of a Data OUT transfer clears the SET bit in the CntOutRegister and the OD bit in the StatusRegister to make the next USB OUT or Setup transfer possible.

Figure 5. OUT Transfer of StatusRegister

Figure 6. Complete Data OUT Transfer

Figure 7. OUT Transfer, only CntOutRegister and OUT FIFO Bytes

Interrupt Function If SIN = 1, the SDO pin can be used to generate an The interrupt latch is reset on reading the status interrupt signal. The interrupt is low active. It is register. If an interrupt is generated during readtriggered if a control transfer is made from the USB ing StatusRegister, this interrupt is latched and host or a control or interrupt transfer is made to the the interrupt source is after new StatusRegister USB host and one of the ID12, ID0 or OD bits has reading visible. been set in the StatusRegister <3-1> or at high A WAKE interrupt is only generated during the stop level of the WAKE pin. An interrupt signal is also state (bits SO and/or SMC in the BridgeConfig triggered on RESUME and USB\_RESET. Register are set).

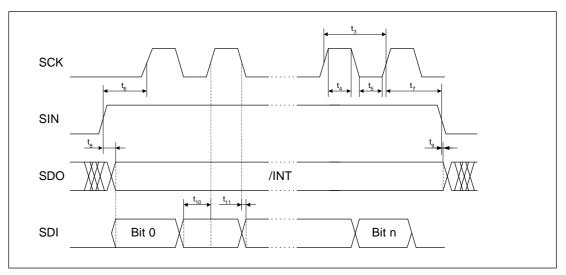

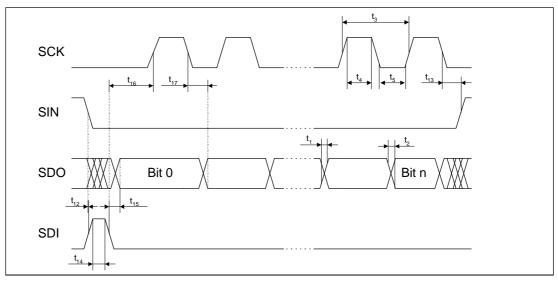

#### Timing Serial Interface

Figure 8 and Figure 9 show the timing of the serial interface of the TH6503. The serial interface is controlled by a standard microcontroller. It can be connected with any microcontroller port.

#### Figure 8. Timing Serial Data IN

Figure 9. Timing Serial Data OUT

**Timing Serial Interface** (continued)

| Description [1]                                           | Symbol          | Unit | min | typ | max  |

|-----------------------------------------------------------|-----------------|------|-----|-----|------|

| General                                                   |                 |      |     |     |      |

| Oscillator Input period on OSC1                           |                 | ns   | 164 |     | 170  |

| Rising time of SDO                                        | t,              | ns   |     | 20  |      |

| Falling time of SDO                                       | t <sub>2</sub>  | ns   |     | 7   |      |

| SCK period                                                | t <sub>3</sub>  | ns   | 600 |     | Step |

| High time SCK [2]                                         | t <sub>4</sub>  | ns   | 345 |     |      |

| Low time SCK [2, 3]                                       | t <sub>5</sub>  | ns   | 255 |     |      |

| Data IN                                                   |                 |      |     |     |      |

| Setup time of SCK after rising edge of SIN                | t <sub>6</sub>  | ns   | 170 |     |      |

| Hold time of SIN after last rising edge of SCK            | t <sub>7</sub>  | ns   | 170 |     |      |

| Setup time of INT-Signal after rising edge of SIN         | t <sub>8</sub>  | ns   |     |     | 200  |

| Hold time of INT-Signal after falling edge of SIN         | t <sub>9</sub>  | ns   | 165 |     |      |

| Setup time of Data on SDI before rising edge of SCK       | t <sub>10</sub> | ns   | 170 |     |      |

| Hold time of Data on SDI after falling edge of SCK        | t <sub>11</sub> | ns   | 0   |     |      |

| Data OUT                                                  |                 |      |     |     |      |

| Setup time of SDI-pulse after falling edge of SIN         | t <sub>12</sub> | ns   | 170 |     |      |

| Setup time of SIN after last falling edge of SCK          | t <sub>13</sub> | ns   | 170 |     |      |

| High time of SDI-pulse                                    | t <sub>14</sub> | ns   | 255 |     |      |

| Setup time of Data on SDO after falling edge of SDI-pulse | t <sub>15</sub> | ns   |     |     | 280  |

| Setup time of SCK after falling edge of SDI-pulse         | t <sub>16</sub> | ns   | 170 |     |      |

| Setup time of Data on SDO after falling edge of SCK       | t <sub>17</sub> | ns   |     |     | 365  |

[1] Capacitive load of 50 pF

[2] Can be asymmetrical

[3] The low time of SCK between the last bit of a byte and the first bit of the next byte must be at least 510 ns.

Input signals are double buffered and digital filtered. Therefore all spikes with a width < 255 ns are suppressed.

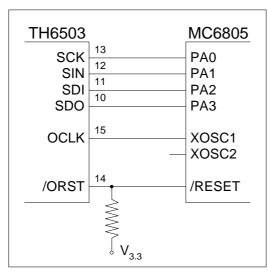

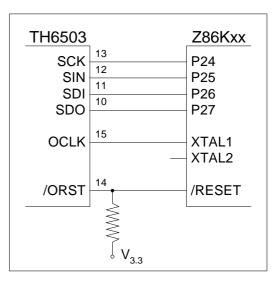

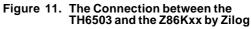

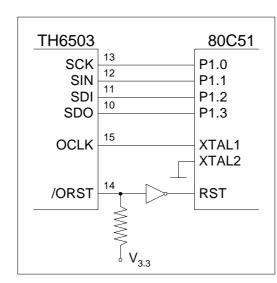

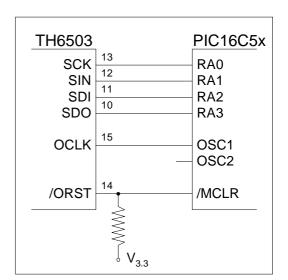

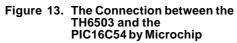

## Connecting the TH6503 with a Microcontroller

The TH6503 can be connected with any microcontroller via a serial interface. The serial outputs can be connected with any microcontroller ports. The TH6503 out clock can be used to provide the clock pulse supply to the microcontroller. The reset output is low active and configured in an open drain structure. For this reason the output must be set at a defined level with external  $\rm V_{_{3.3}}$  resistance.

Figure 10. The Connection between the TH6503 and the MC6805 by Motorola

Figure 12. The Connection between the TH6503 and the 80C51 by Intel

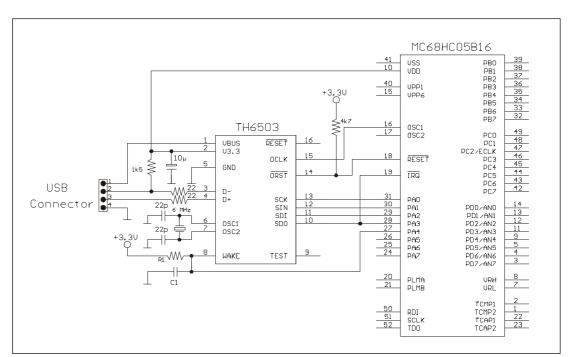

#### Application Wiring Diagram

Figure 14 shows a sample Application circuitry with the TH6503 and a MC68HC05. To stabilize the internal power supply the V3.3 pin must always be connected with an  $10\mu$  capacitor.

Figure 14. Sample Wiring diagram to connect the TH6503 with an MC68HC05

#### **WAKE Function**

The USB specification defines that a device has to go into suspend mode if no bus traffic was detected for ca. 3 ms. After the device is set to suspend mode, the WAKE pin can be used to Wake up the device with an external event.

If the WAKE pin is connected with an RC-Element, the TH6503 wakes up after the time defined by the RC-Element. This feature can be used to check for data in periodical time frames.

#### **RESET** Output

The reset output (/ORST) of the TH6503 can be connected with the reset input of the microcontroller. It's a low active signal.

This signal has a minimum length of 31 clock cycles with a default frequency of 1.5 MHz (see Pin Description for details).

After this reset pulse the microcontroller can reseted but it must wait to programming the TH6503 until the USB reset is inactive.

All register of TH6503 will be held in reset state, exept the StatusRegister, until the corresponding bits HWR or RES is cleared.

#### Register Description

The StatusRegister, CntOutRegister and the OUT FIFO can only be read by the microcontroller. The internal Registers of the TH6503 can only be written by the microcontroller.

#### StatusRegister (read only)

always the first byte of a data out transfer is loaded in the out shift register with the falling edge of an pulse on SDI with SIN=0

| Bit<br>Number | Bit<br>Mnemonic | Reset<br>Status | Function                                                                                                                                                                                                                                                                                                                                 |

|---------------|-----------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7             | HWR             | 1               | Hardware Reset                                                                                                                                                                                                                                                                                                                           |

|               |                 |                 | <ul> <li>is set if the reset source is POR, RESET pin or low voltage reset</li> <li>is reset automatically on reading the StatusRegister and also by the following<br/>SW-Reset before reading the StatusRegister</li> </ul>                                                                                                             |

| 6             | RES             | 0               | USB Reset                                                                                                                                                                                                                                                                                                                                |

|               |                 |                 | <ul> <li>? is set so long as a reset is received on the USB (SW reset)</li> <li>? is reset automatically on reading the StatusRegister and also by the following HW-Reset before reading the StatusRegister</li> <li>? the reset of this bit enables EP0 Out and EP0 In (EO0 and EI0 bits in the SerialFlag Register are set)</li> </ul> |

| 5             | ACT             | 0               | USB Activity                                                                                                                                                                                                                                                                                                                             |

|               |                 |                 | <ul> <li>? is set when the USB is active (all bus states exept IDLE)</li> <li>? is reset automatically on reading the StatusRegister</li> <li>? can be used by the microcontroller to calculate the suspend time</li> <li>? if set the SO and SMC bits in the BridgeConfigRegister are reset</li> </ul>                                  |

| 4             | RDT             | 0               | USB Resume Detect                                                                                                                                                                                                                                                                                                                        |

|               |                 |                 | <ul><li>is set automatically if a resume status has been decoded</li><li>is reset automatically if the resume status has been terminated</li><li>if set the SO and SMC bits in the BridgeConfigRegister are reset</li></ul>                                                                                                              |

| 3             | ID12            | 0               | EP1/2 IN Done                                                                                                                                                                                                                                                                                                                            |

|               |                 |                 | <ul> <li>is set if the data requested by an IN token have been completely transmitted to the USB host and an ACK has been received</li> <li>is reset with the falling SIN edge (end of IN transfer)</li> </ul>                                                                                                                           |

| 2             | ID0             | 0               | EP0 IN Done                                                                                                                                                                                                                                                                                                                              |

|               |                 |                 | <ul> <li>is set if data requested by an IN token have been completely transmitted to the USB host and an ACK has been received</li> <li>is reset with the falling SIN edge (end of IN transfer)</li> </ul>                                                                                                                               |

| 1             | OD              | 0               | OUT Done                                                                                                                                                                                                                                                                                                                                 |

|               |                 |                 | <ul> <li>is set automatically if the data are complete in the FIFO after a valid SETUP or OUT token has been received and an ACK has been sent to the USB host</li> <li>is reset with the rising SIN edge (end of OUT transfer)</li> </ul>                                                                                               |

| 0             | WA              | 1               | WAKE Activity                                                                                                                                                                                                                                                                                                                            |

|               |                 |                 | <ul> <li>is set and reset automatically depending on the voltage level at the WAKE pin</li> <li>is an inverted copy of the WAKE pin and can be used as low active interrupt output, when SIN = 1</li> </ul>                                                                                                                              |

CntOutRegister (read only)

second byte of each out transfer following an OUT packet sync

| Bit<br>Number | Bit<br>Mnemonic | Reset<br>Status | Function                                                                                                                                                                                                                                                                                                                                                     |

|---------------|-----------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-6           | OA              | 0               | OUT Address<br>last valid OUT endpoint<br>? indicates the endpoint of actual OUT FIFO data<br>00 EP0<br>01 EP1<br>10 EP2<br>? only valid if EP1 OUT or EP2 OUT enabled, otherwise the internal<br>Revision number is visible                                                                                                                                 |

| 5             | то              | 0               | Toggle OUT         ? is set if the data packet PID was DATA1 and reset if the data packet PID was DATA0         ? is latched with a valid EP0 SETUP or a OUT Token                                                                                                                                                                                           |

| 4             | SET             | 0               | <ul> <li>Setup</li> <li>is set if a SETUP token is received</li> <li>is reset after OUT transfer to microcontroller</li> <li>no STALL or NAK is sent because it is not permitted on the SETUP token</li> <li>the SO0 and SI0 (STALL EP0) flags in the USBFlagRegister are reset on rising edge of Setup</li> <li>a SETUP token flash all IN FIFOs</li> </ul> |

| 3-0           | OC3-0           | 0               | <ul> <li>EP0 OUT Byte Count</li> <li>amount of OUT data received in the EP0 FIFO in bytes</li> <li>applicable values from 0 to 8</li> <li>a zero data transfer is identified 0</li> </ul>                                                                                                                                                                    |

#### **Internal Register**

Adr/CntInRegister (write only)

first byte of each data in transfer following the IN packet sync

| Bit<br>Number | Bit<br>Mnemonic | Reset<br>Status | Function                                                                                                                                                                                                                                                                                                                |

|---------------|-----------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7             | TI              | 0               | Toggle IN                                                                                                                                                                                                                                                                                                               |

|               |                 |                 | ? is set if the data packet PID is DATA1 and reset if the data packet PID is DATA0                                                                                                                                                                                                                                      |

| 6-4           | RA2-0           | 0               | Internal Address                                                                                                                                                                                                                                                                                                        |

|               |                 |                 | destination address for a write operation to a TH6503 register or IN FIIFO                                                                                                                                                                                                                                              |

| 3-0           | IC3-0           | 0               | IN Byte Count                                                                                                                                                                                                                                                                                                           |

|               |                 |                 | <ul> <li>number of data bytes to be transmitted without Adr/CntInRegister from the microcontroller to the TH6503 if the destination address was an IN FIFO</li> <li>? applicable values from 0 to 8</li> <li>? 0 indicates a zero data transfer to the USB host, but blocks the InFIFO until ACK is received</li> </ul> |

#### EP0/1/2 FIFO (write only)

Internal Address: b000, b001 or b010 Size: 8 bytes

The device user data is stored temporarily at this location for transfer to the USB host.

- the address b000 indicates a data transfer from EP0

- the address b001 indicates a data transfer from EP1

- the address b010 indicates a data transfer from EP2

- only one of the three addresses may be used at any one time; FIFO is used alternately, depending on the device function

- will be flushed with a new SETUP token for as long as bit SET in CntOutRegister is set

#### SerialFlagRegister (write only)

Internal address: b100 Size: 8 bits All endpoints must remain deactivated until USB reset has been decoded (Statusregister <6>).

| Bit<br>Number | Bit<br>Mnemonic | Reset<br>Status | Function                                                                                                                                                                                                                                                                                            |  |  |

|---------------|-----------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7-6           | Х               | 0               | reserved - must be set to 0                                                                                                                                                                                                                                                                         |  |  |

| 5             | EO2             | 0               | Enable EP2 OUT                                                                                                                                                                                                                                                                                      |  |  |

|               |                 |                 | <ul> <li>activate endpoint 2 OUT</li> <li>Microcontroller can set the bit after detecting a USB reset in order to<br/>enable data transfers from the USB host via EP2</li> <li>If set the CntOut Register bit &lt;7-6&gt; indicates the source of the last OUT<br/>transfer binary coded</li> </ul> |  |  |

| 4             | EO1             | 0               | Enable EP1 OUT                                                                                                                                                                                                                                                                                      |  |  |

|               |                 |                 | <ul> <li>activate endpoint 1 OUT</li> <li>Microcontroller can set the bit after detecting a USB reset in order to<br/>enable data transfers from the USB host via EP1</li> <li>If set the CntOut Register bit &lt;7-6&gt; indicates the source of the last OUT<br/>transfer binary coded</li> </ul> |  |  |

| 3             | E12             | 0               | Enable EP2 IN                                                                                                                                                                                                                                                                                       |  |  |

|               |                 |                 | activate endpoint 2 IN<br>? Microcontroller can set the bit after detecting a USB reset in order to<br>enable data transfers to the USB host via EP2                                                                                                                                                |  |  |

| 2             | El1             | 0               | Enable EP1 IN                                                                                                                                                                                                                                                                                       |  |  |

|               |                 |                 | activate endpoint 1 IN<br>? Microcontroller can set the bit after detecting a USB reset in order to<br>enable data transfers to the USB host via EP1                                                                                                                                                |  |  |

| 1             | EЮ              | 0               | Enable EP0 IN                                                                                                                                                                                                                                                                                       |  |  |

|               |                 |                 | activate endpoint 0 (IN transfer)<br>? is set automatically after detecting a USB reset to enable IN control<br>transfers to the USB host                                                                                                                                                           |  |  |

| 0             | EO0             | 0               | Enable EP0 OUT                                                                                                                                                                                                                                                                                      |  |  |

|               |                 |                 | activate endpoint 0 (OUT transfer)<br>? is set automatically after detecting a USB reset to enable OUT control<br>transfers to the USB host                                                                                                                                                         |  |  |

| Size:         | 8 bits          | 5               |                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------|-----------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit<br>Number | Bit<br>Mnemonic | Reset<br>Status | Function                                                                                                                                                                                                                                                                                                                                                                               |

| 7             | F12             | 1               | Flush EP2 IN                                                                                                                                                                                                                                                                                                                                                                           |

|               |                 |                 | <ul> <li>clears EP2 FIFO</li> <li>is set and reset automatically depending on the actual FIFO Status</li> <li>must be set before EP2 of the EP1/2 FIFO can be overwritten by the microcontroller</li> </ul>                                                                                                                                                                            |

| 6             | F11             | 1               | Flush EP1 IN                                                                                                                                                                                                                                                                                                                                                                           |

|               |                 |                 | <ul> <li>clears EP1 FIFO</li> <li>is set and reset automatically depending on the actual FIFO Status</li> <li>must be set before EP1 of the EP1/2 FIFO can be overwritten by the microcontroller</li> </ul>                                                                                                                                                                            |

| 5             | FIO             | 1               | Flush EP0 IN                                                                                                                                                                                                                                                                                                                                                                           |

|               |                 |                 | <ul> <li>clears EP0 FIFO</li> <li>is set and reset automatically depending on the actual FIFO Status</li> <li>must be set before the EP0 FIFO can be overwritten by the microcontroller</li> </ul>                                                                                                                                                                                     |

| 4             | BO0             | 0               | Busy OUT                                                                                                                                                                                                                                                                                                                                                                               |

|               |                 |                 | <ul> <li>blocks the EP0 OUT FIFO for the USB host</li> <li>is set and reset automatically depending on the actual FIFO Status</li> <li>TH6503 responds with no handshake for a USB host SETUP token of with a NAK signal for an OUT token (NAK state)</li> <li>to leave the NAK state, the microcontroller does an OutFIFO read (the microcontroller rereads the last data)</li> </ul> |

| 3             | SI2             | 0               | STALL EP2                                                                                                                                                                                                                                                                                                                                                                              |

|               |                 |                 | <ul> <li>sets EP2 to STALL</li> <li>TH6503 responds with a STALL for a USB host IN or OUT token if address and EP2 have been decoded</li> <li>only operative if EP2 is active</li> </ul>                                                                                                                                                                                               |

| 2             | SI1             | 0               | STALL EP1                                                                                                                                                                                                                                                                                                                                                                              |

|               |                 |                 | <ul> <li>sets EP1 to STALL</li> <li>TH6503 responds with a STALL for a USB host IN or OUT token if address and EP1 have been decoded</li> <li>only operative if EP1 is active</li> </ul>                                                                                                                                                                                               |

| 1             | SIO             | 0               | STALL EPO IN                                                                                                                                                                                                                                                                                                                                                                           |

|               |                 |                 | <ul> <li>sets EP0 IN to STALL</li> <li>TH6503 responds with a STALL for a USB host IN token if address and EP0 have been decoded</li> <li>will be cleared after SETUP token</li> </ul>                                                                                                                                                                                                 |

| 0             | SO0             | 0               | STALL EP0 OUT                                                                                                                                                                                                                                                                                                                                                                          |

|               |                 |                 | <ul> <li>sets EP0 OUT to STALL</li> <li>TH6503 responds with a STALL for a USB host OUT token if address and EP0 have been decoded</li> <li>STALL is inoperative for a SETUP token from the USB host</li> </ul>                                                                                                                                                                        |

#### USBAddressRegister (write only)

Internal address: b110

| Size:         | 8 bits          | 5               |                                                                                                                                                                                                                         |

|---------------|-----------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit<br>Number | Bit<br>Mnemonic | Reset<br>Status | Function                                                                                                                                                                                                                |

| 7             | Х               | 0               | reserved                                                                                                                                                                                                                |

| 6-0           | AD6-0           | 0               | USB device address<br>USB address entered by microcontroller<br>? zero after reset<br>? microcontroller must decode the address from descriptor data after a<br>SETUP (SET_ADDRESS) token and write it in this register |

#### BridgeConfigRegister (write only)

Bits only take effect after the data IN transfer has been completed. Internal address: b111 Size: 8 bits

| Bit<br>Number | Bit<br>Mnemonic | Reset<br>Status | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|---------------|-----------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 6             | OS              | 0               | OCLK Static                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|               |                 |                 | <ul> <li>? is set and reset by microcontroller</li> <li>? if set the OCLK pin drives a static level on the OCLK pin, this level depends on the SMC bit in the BridgeConfigRegister</li> <li>OS SMC OCLK Output</li> <li>0 0 Clock, programmed by OCR&lt;1-0&gt; bits</li> <li>0 1 0</li> <li>1 0 0</li> <li>1 1 1</li> <li>? can be used as ending stop state signal for an external microcontroller with own clock</li> <li>? works like a low active interrupt</li> </ul> |  |  |  |

| 5             | FR              | 0               | Force Resume                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|               |                 |                 | <ul> <li>terminates suspend mode</li> <li>is set by microcontroller if data is sent from connected device</li> <li>the TH6503 signals a Resume to the USB host</li> <li>the timing (10-15 ms) of the Resume State must be done by microcontroller</li> </ul>                                                                                                                                                                                                                |  |  |  |

| 4             | SUS             | 0               | Suspend                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|               |                 |                 | <ul> <li>sets the TH6503 in suspend mode</li> <li>should be set by the microcontroller if no bus traffic is detected for longer than 3 ms</li> <li>can be set and reset by microcontroller only</li> </ul>                                                                                                                                                                                                                                                                  |  |  |  |

| 3             | SO              | 0               | Stop Oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|               |                 |                 | <ul> <li>stops the microcontroller and the USB bridge (the SMC bit is set automatically)</li> <li>? is set by the microcontroller</li> <li>? is reset by an external wake up signal, USB activity or reset</li> </ul>                                                                                                                                                                                                                                                       |  |  |  |

| 2             | SMC             | 0               | Stop Microcontroller Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|               |                 |                 | <ul> <li>stops the microcontroller</li> <li>is set by the microcontroller</li> <li>is reset by an external wake up signal, USB activity or reset</li> <li>only affects the OCLK pin</li> </ul>                                                                                                                                                                                                                                                                              |  |  |  |

| 1-0           | OCR1-0          | 0 0             | Out Clock Rate                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|               |                 |                 | output frequency on the OCLK pin<br>0 0 1.5 MHz (default)<br>0 1 2.0 MHz<br>1 0 3.0 MHz<br>1 1 6.0 MHz, without guarantee of symmetry, it depends on the<br>quality of the oscillation element                                                                                                                                                                                                                                                                              |  |  |  |

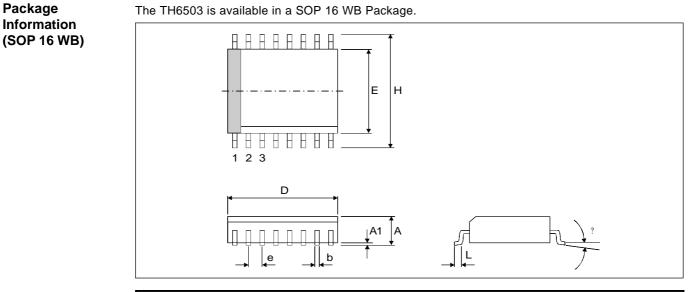

15

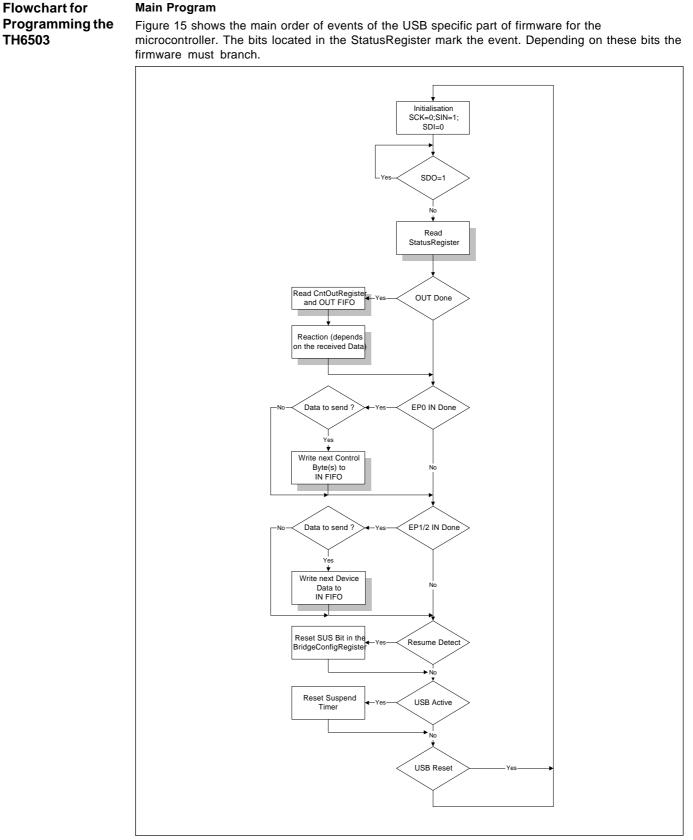

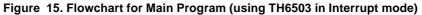

Figure 16. Reading the StatusRegister

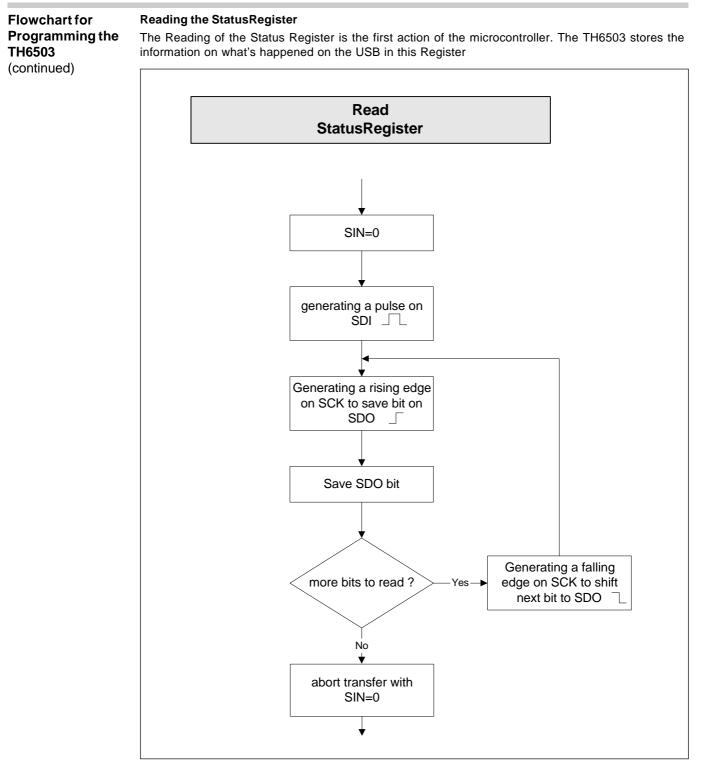

#### Figure 17. Reading the CntOutRegister and OUT FIFO

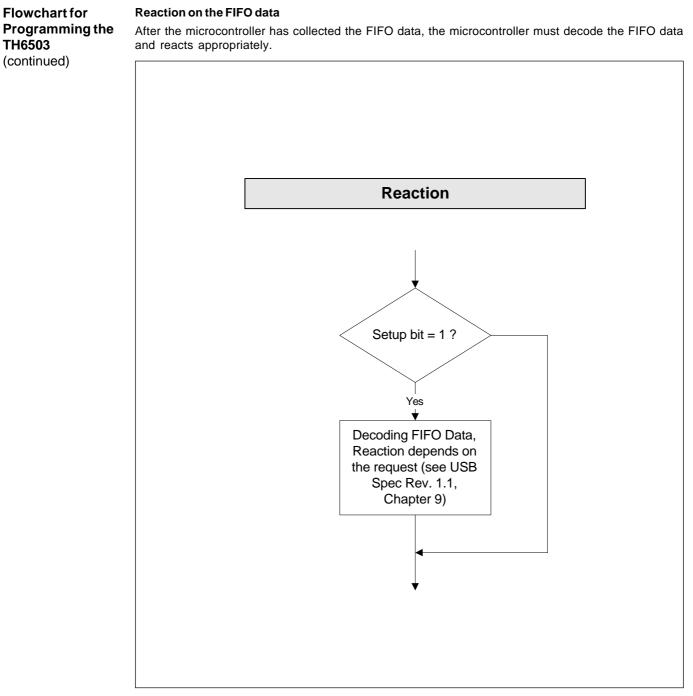

Figure 18. Reaction on the received Data

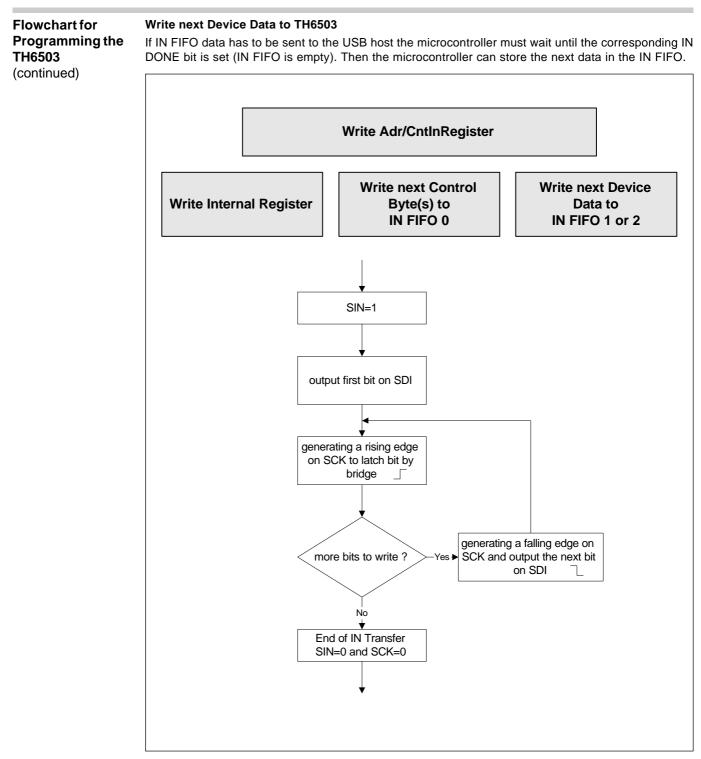

Figure 19. Writing next Device or Control Data to IN FIFO

#### Electrical Characteristics

All voltage values are referenced to GND (GND = 0 V). All values are based on the USB specification V1.1. If any value is unspecified, the value from the USB specification V1.1 is valid.

#### Absolute maximum ratings

| Parameter                           | Symbol            | Min   | Max        | Unit |

|-------------------------------------|-------------------|-------|------------|------|

| DC supply voltage                   | V <sub>DD</sub>   | - 0.3 | 7.0        | V    |

| Input voltage                       | V <sub>IN</sub>   | - 0.3 | V3.3 + 0.3 | V    |

| Input Current                       | I <sub>IN</sub>   | - 10  | 10         | mA   |

| Storage temperature range (ceramic) | T <sub>stgc</sub> | - 65  | 150        | °C   |

| Storage temperature range (plastic) | T <sub>stgp</sub> | - 40  | 125        | °C   |

| Power Dissipation (SOP16)           | P <sub>D</sub>    |       | 600        | mW   |

#### **Recommended Operational Conditions**

| Parameter                   | Symbol          | Min  | Тур  | Max   | Unit |

|-----------------------------|-----------------|------|------|-------|------|

| DC supply voltage           | V <sub>dd</sub> | 4.40 | 5.00 | 5.25  | V    |

| Operating temperature range | T <sub>A</sub>  | 0    |      | 70    | °C   |

| Junction temperature        | TJ              |      |      | < 150 | °C   |

| Operating Frequency         | f <sub>op</sub> |      | 6.00 |       | MHz  |

| Electrical<br>Characteristics | Static Characteristics                     |                      |                                                                  |                      |       |                      |      |  |  |  |

|-------------------------------|--------------------------------------------|----------------------|------------------------------------------------------------------|----------------------|-------|----------------------|------|--|--|--|

| Characteristics               | Parameter                                  | Symbol               | Condition [4]                                                    | Min                  | Тур   | Max                  | Unit |  |  |  |

|                               | Power supply voltage                       | V <sub>3.3</sub>     |                                                                  | 3.00                 | 3.30  | 3.60                 | V    |  |  |  |

|                               | Power supply current                       | l <sub>3.3</sub>     |                                                                  |                      |       | 60                   | mA   |  |  |  |

|                               | Stand-by Current [5]                       | I <sub>STB</sub>     |                                                                  |                      | 80    | 150                  | μA   |  |  |  |

|                               | Voltage input LOW                          | V                    |                                                                  |                      |       | 0.3*V <sub>3.3</sub> | V    |  |  |  |

|                               | Voltage input HIGH                         | V <sub>IHCMOS</sub>  |                                                                  | 0.7*V <sub>3.3</sub> |       |                      | V    |  |  |  |

|                               | Schmitt trigger, positive going threshold  | V <sub>T+CMOS</sub>  |                                                                  |                      |       | 2.4                  | V    |  |  |  |

|                               | Schmitt trigger, negative going threshold  | V <sub>T-CMOS</sub>  |                                                                  | 0.8                  |       |                      | V    |  |  |  |

|                               | Hysteresis, Schmitt trigger<br>(VT+ – VT-) | V <sub>HYSCMOS</sub> | $\rm V_{I\!L}$ to $\rm V_{I\!H}, \rm V_{I\!H}$ to $\rm V_{I\!L}$ | 0.5                  |       |                      | V    |  |  |  |

|                               | Differential Input Sensitivity             | V <sub>DI</sub>      | (D+)-(D-)                                                        | 0.2                  |       |                      | V    |  |  |  |

|                               | Differential Common Mode Range             | V <sub>CM</sub>      | Includes $V_{_{DI}}$                                             | 0.8                  |       | 2.5                  | V    |  |  |  |

|                               | Single Ended Receiver Threshold            | V <sub>se</sub>      |                                                                  | 0.8                  |       | 2.0                  | V    |  |  |  |

|                               | Single Ended Receiver Hysteresis           | V <sub>HYSE</sub>    |                                                                  | 0.1                  |       |                      | V    |  |  |  |

|                               | Input low current                          | l <sub>L</sub>       | $V_N = GND$                                                      | -10                  |       | 10                   | μA   |  |  |  |

|                               | Input with pullup                          | I <sub>ILU</sub>     | $V_N = GND$                                                      | -50                  | -21.0 | -7                   | μA   |  |  |  |

|                               | Input high current                         | l <sub>H</sub>       | V <sub>№</sub> = V3.3                                            | -10                  |       | 10                   | μA   |  |  |  |

|                               | Input with pulldown                        | I <sub>IHD</sub>     | V <sub>№</sub> = V3.3                                            | 7                    | 22.9  | 65                   | μA   |  |  |  |

|                               | Voltage output LOW                         | V <sub>OL</sub>      | I <sub>oL</sub> = 1 mA                                           |                      |       | 0.4                  | V    |  |  |  |

|                               | Voltage output HIGH                        | V <sub>oh</sub>      | I <sub>OH</sub> = 1 mA                                           | 2.4                  |       |                      | V    |  |  |  |

|                               | Current Output                             | l <sub>o</sub>       |                                                                  |                      |       | 1                    | mA   |  |  |  |

|                               | Differential output LOW                    | $V_{old}$            | R <sub>L</sub> of 15 KOhm<br>to GND                              |                      |       | 0.3                  | V    |  |  |  |

|                               | Differential output HIGH                   | V <sub>OHD</sub>     | R <sub>L</sub> of 1.5 KOhm<br>to 3.6 V                           | 2.8                  |       | 3.6                  | V    |  |  |  |

|                               | Hi-Z Output Leakage Current                | I <sub>oz</sub>      | V <sub>N</sub> = GND<br>or V3.3                                  | -10                  |       | 10                   | μA   |  |  |  |

Notes:

[4] Specified at VDD = VBUS = 4.40V to 5.25V and tested at room temperature only

[5] Differential Transceiver fs in Suspend Mode, tested without pull-down and pullup Resistors

on the D- and D+ data line

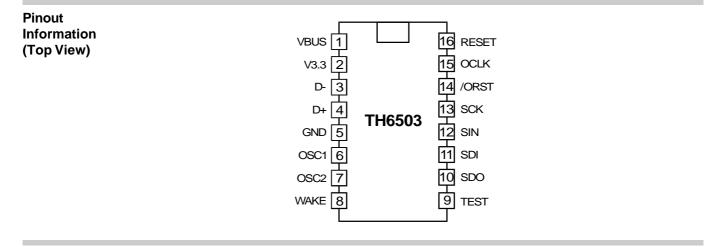

#### **Pin Description**

| Pin Des | scription         |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

|---------|-------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| USB In  | terface           |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| 1       | VBus              | 1             | adjacent 5V bus voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| 5       | GND               | 1             | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| 4       | D+                | 1/O           | USB data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| 3       | D-                | 1/O           | USB data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| Ŭ       | 5                 |               | ? must be connected via 1.5 kOhm resistor to 3.3 V for low speed devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| Microc  | l<br>ontroller Ir | terface       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| 13      | SCK               | 1             | Serial Clock (generated by microcontroller)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

|         | Cont              |               | <ul> <li>? OUT transfer: SDO is accepted by the microcontroller in high status or with falling SCK edge.<br/>The USB bridge shifts the next bit to SDO in low status or with rising edge.</li> <li>? IN Transfer: SDI is accepted by the USB bridge in high status or with falling SCK edge.</li> <li>? The microcontroller shifts the next bit to SDI in low status or with rising edge.</li> <li>? internal pulldown</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| 12      | SIN               | -             | <ul> <li>Serial Input Direction (generated by the microcontroller)</li> <li>? specifies the direction of the data transfer and marks the end of a FIFO transfer</li> <li>? SIN = 0: data is sent from the USB bridge to the microcontroller via SDO. An OUT packet sync for the StatusRegister or CntOutRegister can be triggered via SDI. A rising edge terminates a Status or OUT transfer and the USB OUT Done status bit is cleared.</li> <li>? SIN = 1: Data is sent from the microcontroller to the USB bridge via SDI. SDO emits an /INT signal. A falling edge terminates an IN transfer and the EP0 IN Done or EP1/2 IN Done status bit is cleared if the destination address is a FIFO address.</li> <li>? rising edge indicates the commencement of an IN transfer (IN packet sync). The IN is started once SCK is pulsed. The Adr/CntInRegister is transferred initially.</li> <li>? internal pulldown</li> </ul> |  |  |  |  |  |  |

| 11      | SDI               | I             | <ul> <li>Serial Data IN (from the microcontroller to the USB bridge)</li> <li>? generated by the microcontroller</li> <li>? SIN = 0: the falling edge from a single SDI impulse loads the first bit (LSB first) of the StatusRegisters to SDO.<br/>The StatusRegister can be read. Two SDI impulses load the first bit of the CntOutRegister.</li> <li>? SIN = 1: SDI transfers the serial data.</li> <li>? internal pulldown</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| 10      | SDO               | 0             | Serial Data Out (from the USB bridge to the microcontroller)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

|         |                   |               | <ul> <li>? generated by the USB bridge</li> <li>? SIN = 0: SDO show the Status of bit 0 of the StatusRegister (WA) and after a SDI pulse SDO transfers the serial data.</li> <li>? SIN = 1: SDO is used to generate the /INT signal which can be used to control the microcontroller interrupt</li> <li>? /INT: <ul> <li>Low active signal to SDO at SIN 1</li> <li>is a NOR connection of the RESUME signal, USB reset and an interrupt latch</li> <li>Interrupt latch is set for all increases in OUTDone, EP0 IN Done and EP1/2 IN Done edge.</li> <li>Interrupt latch is reset, if the StatusRegister is read (SDI impulse at SIN= 0).</li> </ul> </li> </ul>                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| 15      | OCLK              | 0             | Clock out for microcontroller (programmable frequency)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| 14      | /ORST             | open<br>drain | <ul> <li>Reset Out (HW- or SW reset)</li> <li>? ORST=0 reset state</li> <li>? ORST=1 normal operation</li> <li>? must be connected with an external pullup resistor (to V3.3)</li> <li>? all resets are indicated on this pin</li> <li>? this type of reset can be determined by evaluating the bits HWR or RES in the StatusRegister &lt;7&gt; or &lt;6&gt;</li> <li>? Reset conditions: <ul> <li>internal POR</li> <li>RESET pin - min. 20µs (31 OCLK cycles at 1.5 MHz) or as long as the RESET pin is active</li> <li>Low voltage reset if VBUS&lt;3.3V ± 10% with a minimum of 20 µs (31 OCLK cycles at 1.5 MHz) or as long as VBUS &lt; 3.3V</li> <li>USB-Reset - reduced to 20 µs (31 OCLK cycles at 1.5 MHz), the end of a USB reset is indicated by a rising edge of /INT and by cleared RES bit in the StatusRegister</li> </ul> </li> </ul>                                                                        |  |  |  |  |  |  |

| Miscell | aneous            |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |